- 内容展现

- 最新评论

AMD开启3D堆叠时代、三星DDR5 512GB

AMD开启多层小芯片时代:今年6月,AMD在Computex上首次展示了配备3D V-Cache的锐龙CPU。而在最近举行的Hot Chips 33上,AMD介绍了更多关于3D堆叠技术的内容。当前有多达10余种小芯片封装架构处于开发中,AMD将针 ... ...

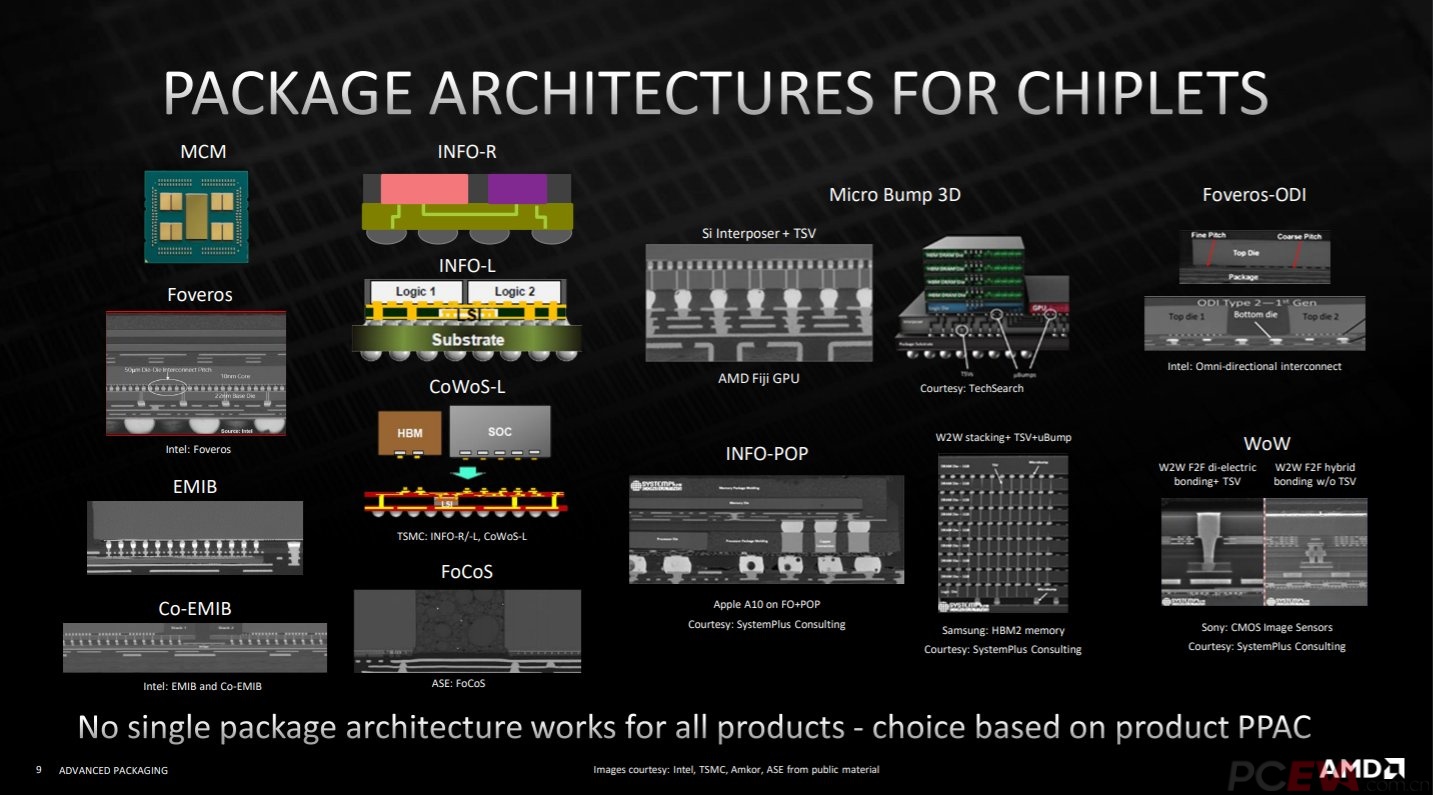

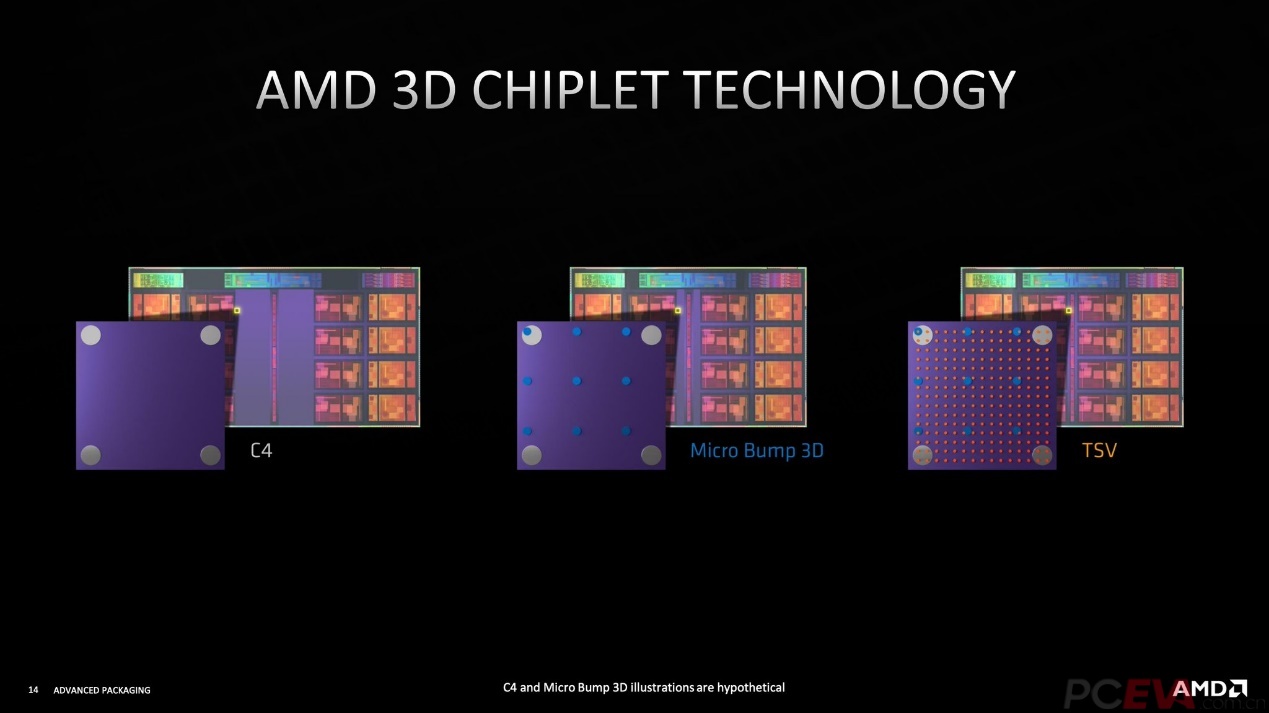

| AMD开启多层小芯片时代: 今年6月,AMD在Computex上首次展示了配备3D V-Cache的锐龙CPU。而在最近举行的Hot Chips 33上,AMD介绍了更多关于3D堆叠技术的内容。 当前有多达10余种小芯片封装架构处于开发中,AMD将针对各自产品的性能、功率、面积和成本来选择不同的封装和小芯片架构。 我们已经在消费类和服务器产品上见到很多2D和2.5D封装的产品,第一款3D Chiplet架构设计将在今年推出:它将在ZEN3 CCD上配备3D V-Cache,不出意外的话就是即将问世的Ryzen 6000处理器。 3D V-Cache是将64MB容量的L3缓存通过TSV堆叠到CCD之上,能够将游戏帧率提高15%,而这只是AMD庞大的3D芯片计划里的第一步。 据AMD介绍,Hybrid键合具具有9u间距,略小于英特尔Forveros互联的10u间距。这一设计相比传统Micron Bump技术的互联能效高3倍以上、互联密度高15倍以上。 在未来,我们将有机会看到更高级的3D芯片堆叠,如DRAM和CPU堆叠、CPU小芯片和CPU小芯片互相堆叠、甚至是核心与核心的堆叠、模块和模块的堆叠。换句话说,芯片的未来将因为3D堆叠技术而大不同。 单条512GB容量的DDR5内存: 4条32GB内存插满,128GB是目前桌面电脑内存容量的天花板。即将到来的DDR5时代将会迎来内存容量的进一步爆发式增长。在HotChips 33上,三星展示了单条512GB容量的DDR5内存条。 三星将8个芯片通过TSV技术堆叠在一起,但减薄芯片和新的硅通孔连接拓扑结构实现了空间上的优化,现在8芯片堆叠的体积比DDR4时代的4芯片堆叠还要小。 三星本次展示的单条512GB内存面向服务器应用,运行频率高达DDR5-7200。 三星预计单条512GB DDR5内存将在今年底前进行量产,而DDR4和DDR5内存的交叉时间点大约会在2023-2024年。 |

本文版权归 PCEVA,PC绝对领域,探寻真正的电脑知识 原作者所有 转载请注明出处

最新评论

热门评论

商家促销

团购试用

原创精华

论坛热帖

468关注

29参与

430关注

28参与

466关注

21参与

447关注

21参与

582关注

18参与

131关注

14参与

265关注

13参与

230关注

7参与

2316关注

6参与

227关注

4参与

精彩图文