- 内容展现

- 最新评论

铠侠刀法:闪存单元一分为二 容量x2

尽管QLC(4bit/单元)尚未普及,铠侠(原东芝存储)已经马不停蹄的在研发PLC闪存(5bit/单元)。近日在铠侠发表Twin BiCS Flash构型时,众人再次看到了PLC闪存的身影。铠侠似乎已经找到了提升PLC闪存可靠性的秘诀 .. ...

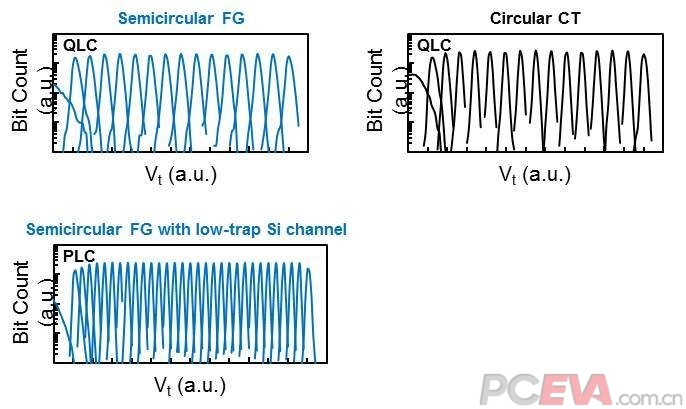

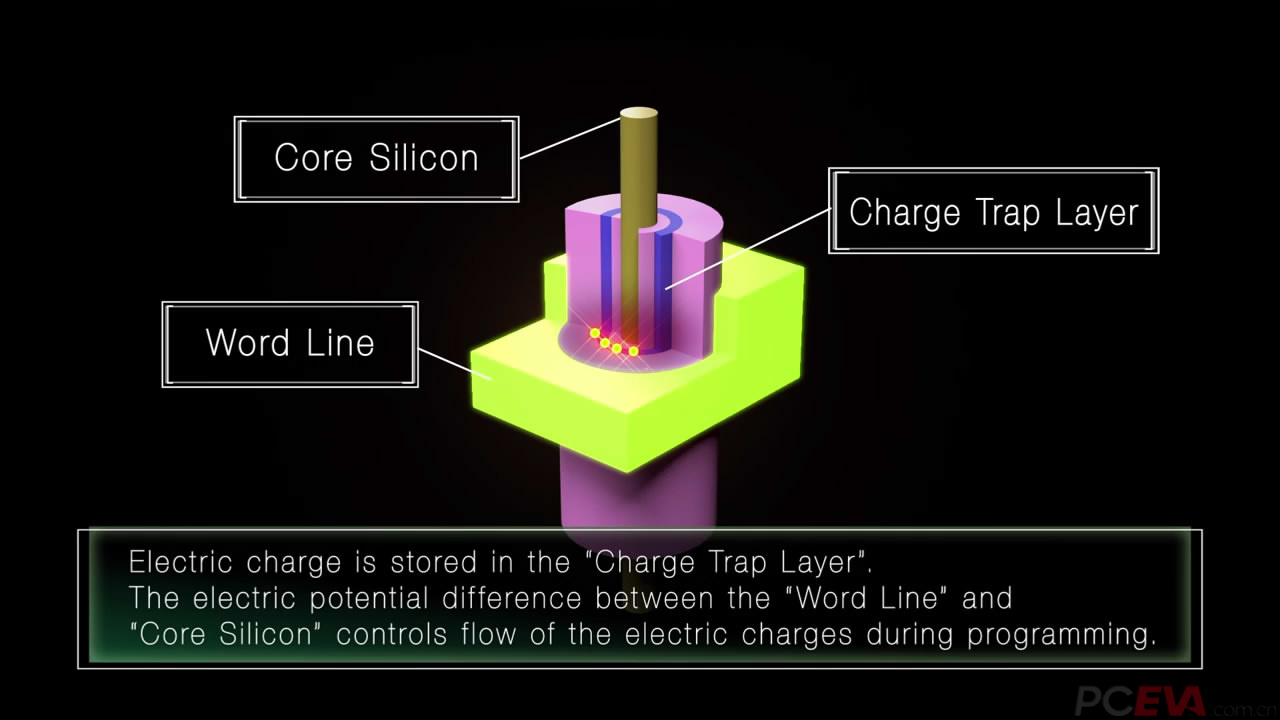

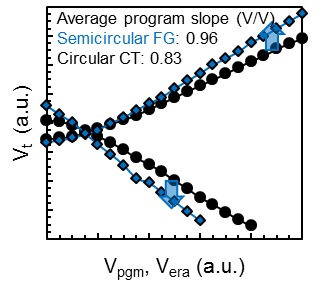

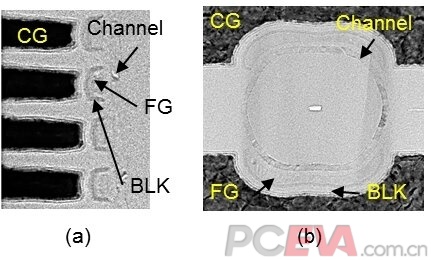

| 尽管QLC(4bit/单元)尚未普及,铠侠(原东芝存储)已经马不停蹄的在研发PLC闪存(5bit/单元)。近日在铠侠发表Twin BiCS Flash构型时,众人再次看到了PLC闪存的身影。 铠侠似乎已经找到了提升PLC闪存可靠性的秘诀:Twin BiCS。这种新技术是将现有圆形的3D闪存单元从中心对称的分割开来,形成两个半圆形部分。下图展现了单个BiCS闪存单元的结构,源自东芝存储视频截图。 据称新设计的Twin BiCS结构能够减少闪存数据写入时间,同时还能降低电子泄露水平,从而提升闪存的性能及可靠性。 通过将闪存单元一分为二,实现存储单元尺寸小型化,由此将带来更大的存储密度,成为继多层单元(MLC/TLC/QLC)、多层堆叠之后又一个全新的发展方向。 Twin BiCS的众多优势听起来非常诱人,但外界并不清楚这种新设计的制造工艺难度,以及具体何时能够实用化,或许会在PLC闪存面世以后。 |

本文版权归 PCEVA,PC绝对领域,探寻真正的电脑知识 原作者所有 转载请注明出处

最新评论

热门评论

商家促销

团购试用

原创精华

论坛热帖

367关注

29参与

329关注

28参与

365关注

21参与

346关注

21参与

251关注

9参与

362关注

4参与

155关注

4参与

71关注

3参与

372关注

3参与

293关注

3参与

精彩图文