- 内容展现

- 最新评论

3D闪存堆叠层数将突破140层

坚果R1的皇帝版8G+1T ROM配置赚足了眼球,借助于当代64层堆叠3D闪存,单芯片封装1T闪存颗粒得以问世,这才让手机达到了移动硬盘级的容量。不过很快手机闪存的容量还将刷新记录,预计明年年初就将有1.5T闪存颗粒。 .. ...

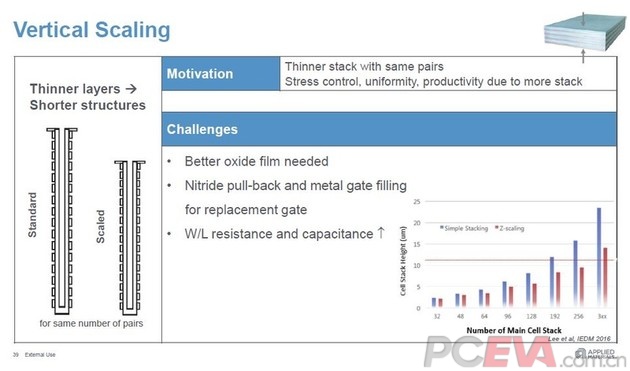

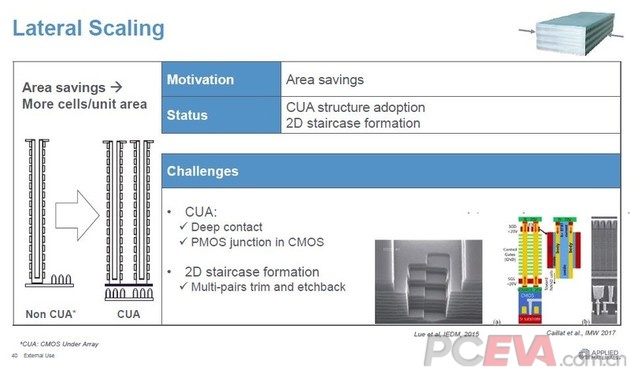

| 坚果R1的皇帝版8G+1T ROM配置赚足了眼球,借助于当代64层堆叠3D闪存,单芯片封装1T闪存颗粒得以问世,这才让手机达到了移动硬盘级的容量。 不过很快手机闪存的容量还将刷新记录,预计明年年初就将有1.5T闪存颗粒。推动容量上升的是3D闪存的堆叠层数。东芝预计96层3D闪存就可以提供768Gb的单晶粒容量,辅以叠Die技术即可实现单颗1.5T的闪存。 最近在日本举行的国际存储研讨会上,来自应用材料公司的Sean Kang介绍了未来3年内3D闪存的技术演进路线。今年年底实现90层以上堆叠,到2020年实现大于120层堆叠,2021年可实现大于140层堆叠。 当然就如同平地建起的大厦一样,没有牢固的根基是无法稳定的拔地而起。随着堆叠层数的增加,3D闪存堆叠高度增长将会给蚀刻技术带来挑战。为应对这一挑战需要压减3D闪存中字线和绝缘膜的厚度,抑制闪存单元堆叠高度的升高速度。 要压减高度的目的,需要在材料和工艺上取得新的突破。而日本恰恰在基础材料研发上拥有优势,就我们所知的英特尔年度供应商奖名单中,提供材料技术支持的日本企业占据半壁以上江山。 就目前的计划来看,闪存制造企业需要克服工艺与材料瓶颈,将字线与绝缘的叠层高度从70nm一步步压低到45-50nm,才能实现大于140层的堆叠高度。除此之外,英特尔/美光已经在他们的第二代64层堆叠3D闪存中应用了CuA(CMOS under Array)技术,这有可能成为未来3D闪存的标配,它是将外围电路置于存储单元阵列之下,进一步提升存储密度。据美光透露,该技术在64层堆叠水平下可提供高达25%的空间节省率,这意味着更低的单位容量成本和更大的闪存容量。 |

本文版权归 PCEVA,PC绝对领域,探寻真正的电脑知识 原作者所有 转载请注明出处

发表评论

最新评论

- 引用 NuclearBomb

- 手机急需扩充容量。 这个不错啊。

- 引用 sss668800

- 有个地方没理解,3D闪存能否理解为2D闪存的叠加?

我看中关村说的:http://news.mydrivers.com/1/477/477251.htm

比如东芝的15nm NAND容量密度为1.28Gb/mm2,而三星32层堆栈的3D NAND可以轻松达到1.87Gb/mm2,48层堆栈的则可以达到2.8Gb/mm2。

貌似相同面积,层数的增加并不是简单的线性比例,难道是举例的制程不同?

如果制程相同,2D是1Gb/mm2,那么64层的3D是否就能达到64Gb/mm2呢?

还有个问题,层数增加除了减少封装的成本以外,还有啥成本减少?

- 引用 Essence

sss668800 发表于 2018-5-18 16:47

有个地方没理解,3D闪存能否理解为2D闪存的叠加?

我看中关村说的:http://news.mydrivers.com/1/477/47725 ...

3D闪存并不是单纯的垂直叠Die(把多个闪存晶粒封装到一个颗粒当中,如果叠die也叫3D闪存,那早在19nm时代就已经有单个颗粒封装16Die的“3D”了),所以层数和容量并非线性增长。另外3D闪存的制程和2D的确是不同的,更重要的是它们的结构也完全不同,无法直接对比。

热门评论

商家促销

团购试用

原创精华

论坛热帖

367关注

29参与

329关注

28参与

365关注

21参与

346关注

21参与

251关注

9参与

261关注

4参与

155关注

4参与

372关注

3参与

293关注

3参与

346关注

2参与

精彩图文